なぜいま、東大が半導体の設計研究センターd.labを創設したのか

(2020年3月20日 10:22)東大が2019年10月に半導体の設計研究センターd.labを創設、11月には世界トップの半導体製造請負ファウンドリ、台湾TSMCとの業務提携を交わした。なぜ今、また半導体なのか。センター長を務める黒田忠弘教授(図1)は、国内の電機業界からそのように言われたという。

図1 慶應義塾大学から東京大学に招かれたd.labセンター長の黒田忠弘教授

GAFAと呼ばれる、グーグル(G)やアマゾン(A)、フェイスブック(F)、アップル(A)とMicrosoftなどのITサービス企業がみんな半導体チップを作り始めている。いやアップルはiPhoneとiPadに向けた半導体開発を2006年ごろから始めていた。なぜ、こういったところが自分の半導体を持つようになったのか。主な理由は三つある。一つは自分の半導体によってクラウドに使うデータセンター向けのコンピュータの消費電力を1桁下げられること。もう一つは半導体設計言語を知らなくてもデザインハウスで設計してもらえるようになったこと、そして、何よりも独自の半導体で競合相手との差別化できることだ。パソコンの父といわれるアラン・ケイ氏の言葉にもある、「ソフトウエアに打ち込む人はハードウエアも作りたくなる」と。

何よりも自分の半導体を持つために、昔は工場が必要だったが、今は設計だけのファブレスで済むようになった。製造だけのファウンドリというビジネスが確立したため、自分で半導体工場を持たなくても済むようになった。DRAMやNANDフラッシュのようなメモリは昔ながらの大量生産ビジネスだから、メーカーは自分で工場を持つが、システムLSI(SoC: System on Chip)は自分専用の半導体チップで少量生産であるため自社工場を持つ必要がない。ファウンドリに頼めばよい。

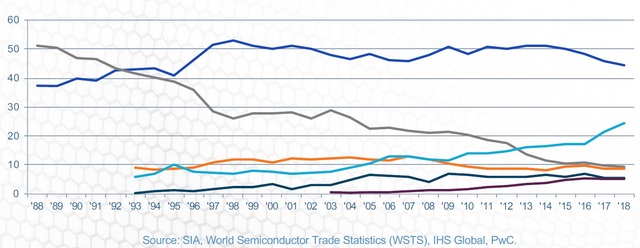

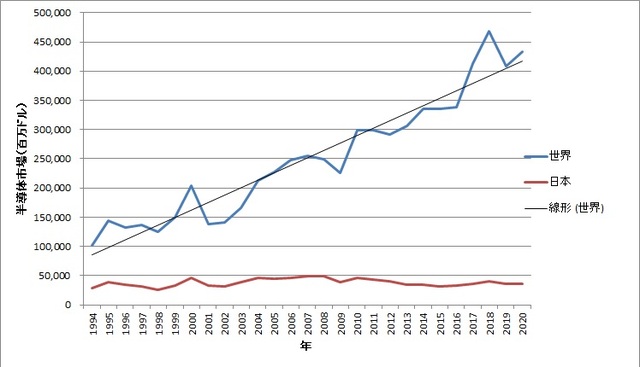

世界の半導体はシステムLSIで成長しているのに、日本だけが成長していない(図2)。DRAMを捨て、システムLSIに路線を変更したのにもかかわらず、相変わらずDRAM同様の大量生産ビジネスを展開していた。少量多品種に合わせて工場を縮小して少量でもコスト的に対応できる工場にしていなかったからだ。日本だけが垂直統合にこだわり続け、製造のプロセスエンジニアは、少量生産は半導体ビジネスに合わないとして低コスト技術を開発しなかった。大量生産できるシステムLSIなどは存在しないのにもかかわらず、垂直統合を捨てようとしなかった。

図2 世界の半導体市場は成長し続けているのに日本市場だけが成長していない 2018年には日本半導体の世界シェアは9%まで落ちた 出典:GSA、2019 SIA Factbook

メモリを作らないのなら、ファブレスを目指すべきで、さもなければ、自社以外の多くの半導体メーカーから注文を取ってくるファウンドリをすべきだった。ところが、どちらも中途半端だったために、徐々に没落するという最悪のパターンに陥った。これは自社の半導体部門に対してシステムLSIへ向けよ、と指導した当時の経済産業省と総合電機の経営者が半導体ビジネスについて無知だったためと言わざるを得ない。

加えて、日本の半導体メーカーは、総合電機会社の一部門あるいは子会社にすぎず、主体的な経営が許されない状況にあった。半導体がITのテクノロジーの源であることを総合電機の経営者たちは理解できなかった。その割に半導体部門を支配し続けた。今でもその姿勢は変わらない。2020年になって東芝は、HOYAが高い価格で、東芝の子会社であるニューフレアを買ってくれると提案したのにもかかわらず、なんの相乗効果も生まないニューフレアをTOBで買い戻すことに躍起になっていた。まるで駄々っ子が欲しくもないお菓子を誰かが取ろうとしたら、それは自分のお菓子だとごねる様子とそっくりだった。半導体業界関係者は今でも、東芝がなぜあれほどまで躍起になってニューフレアを買い戻そうとしたのかわからない、と述べている。

そのような総合電機の経営者は今でも半導体ビジネスを理解できていない。だから、総合電機の経営者は、なぜ今半導体なのか、全く理解できていないのである。東大の黒田センター長が昨年まで勤務していた慶應義塾大学では、半導体研究には優秀な人材が来るが、卒業生は半導体メーカーに行かなかった、という。日本の従来の半導体メーカーの親会社があまりにも情けなかったからだ。黒田センター長は、慶応大学に招聘された2000年まで東芝にいた優秀な半導体エンジニアであり、世界的な国際会議でも何度か招待講演をしていたほどの半導体の達人である。

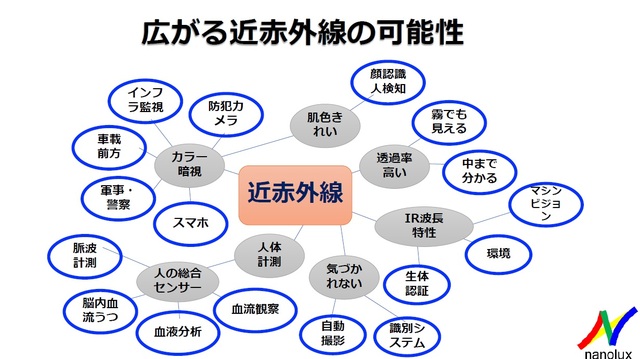

幸いなことに、総合電機とは関係なく、日本でも半導体を求める流れが確実にできつつある。AIフレームワークのChainerを開発してきた、東大発ベンチャーのプリファードネットワークスは学習向けのAIチップを開発(参考資料1)、グラフィックスに強いIPベンダーのDMP(デジタルメディアプロフェッショナル)、最先端の5nmプロセスを用いてAIチップの前段となるIPを開発したTRIPLE-1(参考資料2)、フルHDのカラー赤外線映像を再現できるカラー赤外線センサを開発したナノルクス(参考資料3)など、いずれもファブレス半導体メーカーの仲間入りを果たした。全て将来性のある半導体チップメーカーである。しかも全てファブレス半導体だ。

黒田センター長が半導体設計の研究センターを作る狙いは、ファブレス半導体で勝負できると燃えている、こういった先進のベンチャー企業が登場してきて、そこに日本のファブレスがさらに参入・活躍できる機会がようやく訪れるようになってきたからだ。半導体ビジネスをやる以上、世界のトップメーカーになる気持ちが必要だ。先に述べた新しいファブレス半導体の人たちは全て独自の技術で独自の狙いを掲げている。

黒田センター長はGAFAが専用半導体を設計している様子を見て、これからはやはり専用半導体チップで差別化を図る時代になってきたと見ている。これまでは、専用半導体は価格が高い、複雑で設計に時間がかかる、数量が出ない、などの理由から、日本では冬の時代を20年続けてきた。しかし、これからの専用半導体SoCで、これまで汎用半導体を搭載するシステムの消費電力を1/10に減らす、という目標を同氏は掲げている。

システムの低消費電力化は地球環境のサステナビリティに有効であると同時に競争力も増す。同じシステムで消費電力の低いチップだと、空調が楽になったり不要になったりする。余分な電力を食わない分だけ性能をさらに上げることもできる。低消費電力化は、半導体技術全体の流れとも一致する。

そして、複雑なLSIを短期間で設計するための高位のシステム設計技術を開発し、設計期間を1/10に減らし、低コスト化につなげる、としている。しかも従来のSoCの設計ではHDL(ハードウエア記述言語)やVerilogなどと呼ばれる特殊なLSI設計言語で書かなければならなかった。これをC/C++やPythonなど、なじみのある言語で設計できるようなコンバータ(あるいはコンパイラ)も開発していく。要は誰でもシステム設計できるような抽象度の高い言語で設計できるようにLSI設計を「民主化」する。そのために半導体設計ツールの国内トップエンジニアを招く予定だ。

TSMCと提携した理由は、d.labで開発された設計ツールを用いて設計した半導体チップをTSMCで製造依頼できるからだ。今の日本には製造を請け負うファウンドリが1社もない。TSMC並みの製造技術力を持つファウンドリ会社が日本で生まれれば、当然そのような企業にもビジネス機会ができる。

半導体設計研究センターのd.labのDはDigitalやDataだけのDではない。AIのアルゴリズム研究者やソフトウエア開発者、半導体製造プロセス技術者、ファンド、OEMクルマメーカー、ティア1サプライヤ、ITサービス業者、通信キャリアなど、さまざまな業種や大学関係者などが、企業の壁を越えて自由に夜が更けるまでディスカッションできる場となるDormitoryのDでもある。もちろん専用ICを意味するDomain-specificのD、ゲームチェンジを引き起こすDisruptionのD、DeviceのDでもある。

参考資料

2. 国産ファブレス半導体スタートアップ、5nmのAIチップを開発

(2020/03/20)

「I will Survive」はムーアの法則にも当てはまる

(2020年3月14日 21:21)「I

will Survive(生き残ってやる)」。1980年代のディスコを席巻した歌の一つだ。グロリア・ゲイナーが歌う失恋から立ち上がるその歌は、ディスコテック・ロックの一つとして今でも米国のイベントで流れることが多い。

半導体の世界でもムーアの法則は生きていた。半導体チップに集積されるトランジスタの数は、18~24カ月で倍増する、というムーアの法則だ。ムーアの法則は、もともと半導体企業の先駆者であった米Fairchild

Semiconductor(現在はON

Semiconductorに買収された)に在籍していたゴードン・ムーア氏が1965年、市場に出ている半導体チップのトランジスタ数は毎年2倍に増えているという経済法則を見つけたことから、言われ出した。

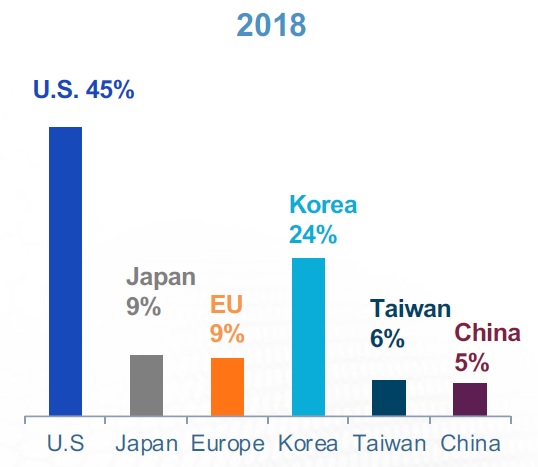

図1は、半導体回路に集積されるトランジスタ数の推移を単純に描いたものだ。縦軸は対数スケールであるから、対数で直線だということは年率何%あるいは何倍で伸びているという意味である。これは市場調査会社のIC

Insightsがグラフ化したもの。ムーアの法則はもう成り立たない、と言われながら、なぜ続いているのか?

図1 半導体に集積されるトランジスタ数は増加し続けている 出典:IC Insights

もちろん、データに偽りはない。ムーアの法則は、毎年2倍から12~18カ月に2倍、あるいは18カ月から24カ月に2倍というように言われるようになり、少しずつ形を変えていった。

最も顕著な変化は、微細化=ムーアの法則、といった捉え方をされるようになったことだ。数nm以下になると、ムーアの法則は死ぬと言われていた。トランジスタ数ではなく微細化技術をムーアの法則と指すようになった。

なぜそうなったか。1980年頃、IBM T. J. Watson研究所にいた、ロバート・デナード(Robert Dennard)博士が打ち立てたスケーリング理論(最近ではデナードの法則という言葉も登場している)に基づいている。これは、MOSトランジスタのドレイン電流が、WµC/L*V2に比例する1次元動作近似をベースにして、トランジスタの寸法を表すW(ゲート幅)、L(ゲート長)、µ(キャリヤ移動度)、C(ゲート容量)を比例縮小したら、動作速度や消費電力がどちらも好ましい方向に行くことを理論づけた。

この理論によれば、微細化すればするほど性能は上がり消費電力が下がるという幸運な特性を持つことがわかった。このため、MOSトランジスタの微細化技術はどんどん進んでいった。半導体の高集積化にとって微細化は常識になった。このため、28nmくらいまでは、ひたすら微細化してきた。言葉が変質したのは、半導体製造のITRS(International Technology Roadmap for Semiconductors)ロードマップの指針であろう。ITRSは、微細化が限界に近づいたから、ムーアの法則は成り立たなくなってきた、と表現した。このため、10年前には「More Moore」や「More than Moore」と言われるようになった。すでに「微細化=ムーアの法則」という言葉に変わってしまっていたのである。

半導体製品は3次元に向かった

図1に見るように、半導体に集積されるトランジスタの数は年率十数カ月で2倍になるという本来のムーアの法則は、実は変わっていないのである。

なぜこうなったのか。半導体に集積するトランジスタを従来の2次元から3次元に変えたからだ。図1の最近の高集積なICはNANDフラッシュメモリである。これは数年前から2次元から3次元へ変更し、それも当初の32層から64層、さらに96層へと高層化してきたのである。トランジスタ数は急速に上がってきた。

これを今度はチップ同士の接続というように3D(3次元)ICとし、スタック(重ねた)したチップを一つのモールドでパッケージすると、外見は1個のIC製品に見える。この3D-ICはムーアの法則に沿うだろう、その定義が最初のゴードン・ムーア博士のままであれば。そうすると、ムーアの法則はまだ当分続くことになる。

(2020/03/14)

大学発ベンチャー誕生を思い出せ、全学挙げて産学共同を推進する東工大

(2020年3月 5日 00:47)磁気テープで有名になったTDK。テープだけではなくコイルやトランスの磁心などに使われるフェライトで有名な会社だ。もちろん、HDD(ハードディスク装置)の磁気ヘッドでも大きく成長した。だが、TDKが東京工業大学から生まれた大学発ベンチャーであることは意外と知られていない。一方の東工大もベンチャーを生み出す気風には至っていない(注)。

日本の産業界を活性化する上で、大学発ベンチャーを成功に導くことは重要なミッションだ。ようやく最近、大学と産業界が手を組む産学共同が日本でも始まろうとしている。これまでは大学の教授や研究室が企業と協力しながら研究を進めてきたケースはある。文部科学省からの予算だけでは不足するため自主的に企業と手を組んだ研究室や教授であったが、全学を挙げて産学共同に取り組んでいたわけではなかった。

東京大学は最近、AI(人工知能)チップを設計するための施設を作ったり(参考資料1, 2)、ファウンドリ事業で世界トップの台湾TSMCと提携したり(参考資料3)してきた。学長自ら旗を振り外部企業との提携や共同プロジェクトを進めてきた。東工大も負けずに全学を挙げて産学協同に取り組み始めた。このほど「第1回東京工業大学国際オープンイノベーションシンポジウム」でその枠組みについて発表した。

東工大の産学共同プログラムは、一種のR&Dコンソーシアムを基本としており、このコンソーシアムに参加する企業や外部機関のパートナーは、これまでの特許やIPとは違う仕組みを取り入れた。この特許の仕組みが最大の特長だ。これまで産学共同が進まない最大の理由が特許であった。国立大学である以上、文科省の管轄下にあり、大学が企業との共同研究では特許は全て文科省、すなわち国庫に入った。このため企業の中には、特許が入手できないのなら自分たちだけで研究した方が良い、と考えるようになった会社も多い。だから産学共同は思うように進まなかった。

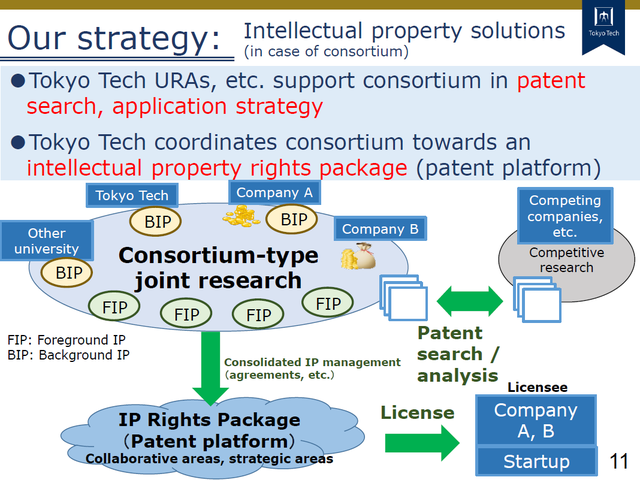

そこで、東工大は従来の仕組みを改めて、共同研究での契約が独占使用かそうではないか、あるいは第三者が使いたいという非独占的な場合の扱いも発明企業と大学の双方の利害に照らして、特許の扱いをフレキシブルに対応できるように変えた(図1)。これによって、これまでのように発明成果を国家に一律に取り上げられることはなくなった。

また、数社が参加する一つのプロジェクトに対して、その中から生まれた特許に関しても担当した企業同士で共有できるようにし、事業化する場合の権利をパッケージ化した特許プラットフォームを作り(図2)、共同開発したテーマの特許を共有できるようにした。これら特許のフレームワークについては文部科学省も理解を示しているようで、2020年2月に開催されたシンポジウムで文科省の来賓あいさつがプログラムに組み込まれていた。

図2 コンソーシアムでは特許を共有、メンバー企業は優先的に使える 出典:東京工業大学

図2 コンソーシアムでは特許を共有、メンバー企業は優先的に使える 出典:東京工業大学

かつて取材した英国のBristol大学やCambridge大学では(参考資料4)、教授をはじめとするアカデミアの人たちは特許には全く関心を示さなかった。共同開発であってもその研究から生まれた成果を特許申請して、権利を受けるものは企業だという考え方であった。アカデミアの人たちは特許を書くことに興味はなく、それよりも学会や国際会議で発表する論文を書く方が研究内容を評価されるため、論文執筆に精力を注ぐ。企業は、利益を追求するため、特許は企業にとって利益の源泉になりうる。例えばQualcomm社は製品を開発する会社と、特許をビジネスとしている会社の2社から成り立つホールディングカンパニーである。

今の東工大の新しい特許のフレームワーク(図2)では、特許の申請は企業が行い、その利益の配分は双方で決めるという考え方だが、これでも英国の共同研究における考え方とは違う。英国の共同研究では資金を提供するのは企業側であり、大学側はそれを受けて研究成果を提供するから、特許化するのは企業側が主体であり、その権利を行使するのも企業側だという考えによる。

しかし米国にはStanford大学のように名門私立大学が多いが、産学共同プロジェクトでは、特許を管理する管理部門が大学にもある。もちろん、Stanford大学の教授たちも日本の教授と同様、特許より論文執筆に精を出す。しかし、特許に関しては私立大学である以上、大学といえども企業と同様ビジネスモデルを常に考えながら進んでいく。研究成果を事業化する場合も管理部門が責任を持つ。今回の東工大の特許の考え方は、Stanford大学に近い。

注)セキュリティソリューションで有名なソリトンシステムズ社は東工大で博士号を取得した鎌田信夫氏が創業したベンチャーであるが、博士号を取得した時の研究テーマである磁性半導体をビジネスにした訳ではないので、大学発ベンチャーとは言えない。

参考資料

1. IBM, AIチップ開発エコシステムとニッポン(2019/2/17)

2. 東大のAIチップ設計拠点が活動開始、カギはデザインハウス(2019/2/28)

SUMCOや東京エレクトロンがTVコマーシャルを出す理由

(2020年2月25日 23:15)最近、半導体がテレビのコマーシャルに出ている。シリコン結晶を製造し、薄くスライスしたウェーハを生産している日本のSUMCO社、半導体の薄膜形成装置や洗浄装置などの半導体製造装置を生産する東京エレクトロンなどが半導体を全面にTV広告を打っている。10年前には考えられなかった。半導体は斜陽産業と新聞でも言われたからだ。

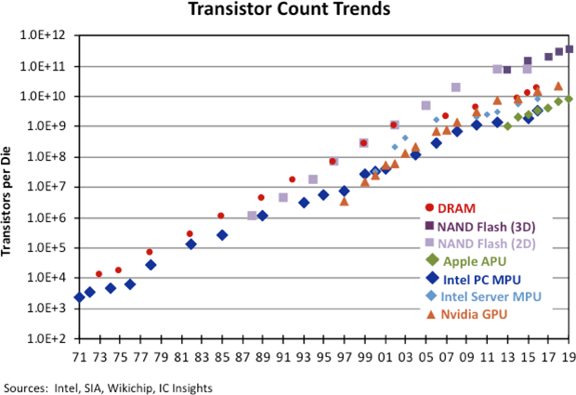

しかし、半導体で利益が出なくなった最大の原因は、総合電機の経営者が半導体産業を理解せず、ひたすら「お上」のいうことを聞いていて、自分のアタマで考えなかったからだ。筆者が「半導体、この成長産業を手放すな」と題した本を日刊工業新聞社から出版したのは今から10年前の2010年だ。半導体は成長産業だったのにもかかわらず、斜陽産業と決めつけ、ひたすら半導体事業を子会社にしたり他社と合体させたりするなど、処分した。ところが、世界の半導体産業は成長し続けているのにもかかわらず、日本だけが停滞していたのである(図1)。その兆候は2010年でも見られている。だから本のタイトルをそのようにした。

図1 半導体市場、世界は成長を続けながら日本だけが停滞している 出典:WSTSの数字を元に筆者がグラフ化

この図はWSTS(世界半導体市場統計)という半導体の工業会のような組織が集めた半導体チップの市場を示したものだ。ここでの市場は、半導体製品を顧客なり販売代理店(ディストリビュータ)なりに手渡した地域を指している。つまり半導体製品を使う人、すなわち家電メーカーや総合電機メーカーなどのいる地域となる。半導体を作るメーカーではない。つまり、総合電機や家電メーカーが半導体を使わなくなったともいえる。実際、ソニーやパナソニック、東芝、日立製作所、NEC、富士通、シャープなど日本を代表していた電機メーカーは半導体を消費せずに製品やサービスを提供しているのである。

これらのメーカーのほとんどが、ここ10年ずっと減収でやってきた。つまり成長していないのである。ただ、収支は赤字から黒字へ転換したものの、リストラを繰り返してきて利益は上がっただけにすぎない。売り上げが伸びていない。すなわち成長していない。

世界は今、半導体でAI専用チップを作り、データセンターやエッジでの電力効率を上げようとしている。グーグルやアップル、フェイスブック、アマゾン、マイクロソフトなどは半導体チップを自社開発している実態を、2020年2月4日号の週刊「エコノミスト」の特集で紹介した。すなわち世界をリードしているGAFAと呼ばれるこれらのITサービス企業が半導体を持つようになっているのである。

日本の総合電機はなんて感度の鈍いことか。半導体は、競合他社との差別化を図るためのツールである。賢いアルゴリズムやソフトウエアはもちろん差別化できる強力なツールではあるが、ソフトウエアはフレキシビリティがあるという強みはあるが、性能が遅い、という弱点がある。半導体チップはこの弱点を補えるツールなのだ。半導体にアルゴリズムを焼き込めばその性能は飛躍的に向上する。それもFPGAのようにプログラムできて、しかもハードワイヤードで高速の性能を得ることができる半導体デバイスもある。

日本の総合電機に半導体を納めていた企業は、もはや日本ではなく海外に目を向けている。海外売り上げの方が圧倒的に多いのである。半導体テストシステムを生産している日本のアドバンテスト社(旧タケダ理研)は、売り上げの92%以上が海外というグローバル企業である。もちろんSUMCOや東京エレクトロンも海外比率の方が圧倒的に多い。だから今でも成長を続け、テレビコマーシャルで半導体が成長産業であることを訴求し続けている。半導体は斜陽産業だと風潮していた総合電機の経営者と、それを聞いて取材していたマスメディアによって作られた斜陽産業のイメージを払拭するために、である。優秀な学生のリクルーティングのためにテレビコマーシャルで、成長産業である半導体を訴求しているSUMCOや東京エレクトロンは、これからも成長し続ける。顧客が海外だからである。

(2020/02/25)

最新の言葉使いに注意!:IoTはエッジからエンドポイントへ

(2020年2月24日 20:49)真っ暗闇でカラーの赤外線画像・映像を撮る

(2020年2月21日 20:19)まず図1を見てほしい。この写真は、真っ暗闇の中で赤外線センサを使って撮ったものだ。真っ暗闇すなわちゼロ・ルクスの明るさでも赤外線を使えばカラー写真は撮れる。しかし、これまでの赤外線センサで撮ると、図1の左のようにモノクロでしか撮れなかった。日本発、赤外線センサ技術のスタートアップ企業であるナノルクス社は、赤外線センサチップを試作、すでに写真撮影のデモを済ませ、実用段階に近づけた。

図1 真っ暗闇で撮った赤外線カラー画像 出典:ナノルクス

これまで赤外線カメラといえば、冷却が必要で、数十万円以上もする高価なぜいたく品だった。ごく一部の応用(特殊な宇宙・防衛、医療関係など)でしか使われてこなかった。また従来の赤外線カメラは、高価であるゆえに画素数を減らして低分解能な写真しか商用化できなかった。

ところが、ナノルクス社のセンサは安価にできる。従来のスマートフォンやデジタルカメラで使われるセンサと、さほど変わらないコストで製造できる。しかも、HD(高解像度)画像を撮影できる。つまり、iPhoneやデジカメなど、これまでの可視光カメラをそのまま赤外線カメラのように使えるのである。加えて、動画も可能だ。赤外線カメラやセンサの破壊的イノベーションといえる。

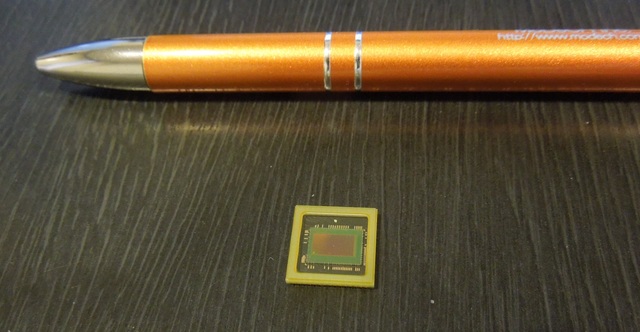

今回、ナノルクス社が開発したこの近赤外線センサは、200万画素のフルHD(1920×1080画素)に近赤外線フィルタを設けた簡単な構造をもち、半導体用のパッケージに実装したものだ。シリコンウェーハ、カラーフィルタ、ICパッケージからなるセンサで、パッケージングした写真(図2)でも、ごく普通のセンサのように見える。赤外線イメージセンサの画素ピッチが3µmであり、監視カメラなどに普通に使われており特に難しい技術ではない。ICパッケージ内の真ん中に見える薄いピンクの部分がチップである。

図2 カラー赤外線CMOSイメージセンサ写真 筆者撮影

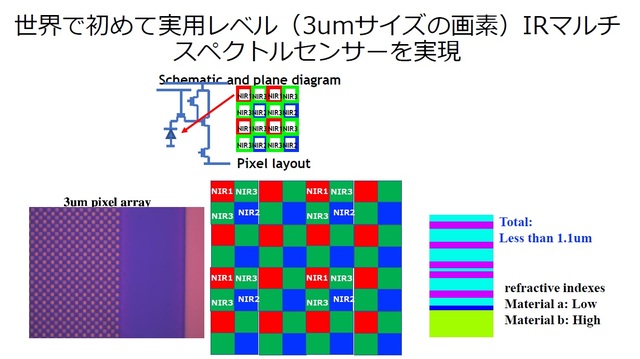

なぜ、カラーの赤外線画像が得られるのか。そのキモはカラーフィルタにある。可視光のカメラは、可視光のRGB(赤緑青)の色の3原色のカラーフィルタを通してカラー写真を撮れているが、この赤外線カメラでは、可視光のRGBに相当する赤外線の3原色を利用した。それを近赤外(Near Infrared)なので、NIR1(波長800nm)、NIR2(波長870nm)、NIR3(波長940nm)に相当させて(図3)、カラーを実現した。元々は産業技術総合研究所のエンジニアが見つけたため、そのまま社員として創業時から一緒に実用化に向けて開発に取り組んできた。

図3 近赤外線NIR1、NIR2、NIR3の3原色でフルカラーを実現 出典:ナノルクス

カラーフィルタといっても赤外波長なので色が見えるわけではないが、便宜上NIR1、2、3として表現し、カラーフィルタに配置した。NIR1~3はそれぞれフィルタを構成する訳だが、ここでは多層膜をパターニングすることで1画素内にそれぞれを配置できるようにした。基本的な考え方は、透過率の異なる2種類の膜を交互に積み重ねて10層程度積むと波長選択性を持つようになる。つまりフィルタができる。いわゆる、ファブリ・ペロー共振器である。

そして3種類の波長に対応させるためには、真ん中の膜のみ厚さをそれぞれ変えていくのだという。他の膜の厚さは変えなくてもよいため、低コストで製造できる。ここに3µmピッチのパターンが必要になる。これにより、それぞれNIR1、NIR2、NIR3の「近赤外波長の色」になるという訳だ。これらの膜を10層形成しても1.1µm以下の厚さで済む。一般の可視光カメラのカラーフィルタの厚さに近い。だから、安いコストで実現できるのだ。

CMOSイメージセンサIC回路の試作ではファウンドリに依頼し、カラーフィルタのパターニング加工は産総研、パッケージングは韓国メーカーに依頼した。量産時には生産数量にもよるが、生産能力のあるファウンドリにイメージセンサ回路やカラーフィルタ、そしてパッケージングのOSATに依頼するようだ。

図4 カラー近赤外イメージセンサが描く応用例 出典:ナノルクス

カラー赤外線イメージセンサチップ全体で、数ドルにしたいという。数ドルなら、これまでとは違う全く新しい用途が開けてくる。特にメディカル・ヘルスケア向けの用途は大きく、セキュリティや生体認証などさまざまな応用が可能になってくる(図4)。いよいよ実用化に近づいたことで次のラウンドの資金調達したい、と社長の祖父江基史氏は意気込んでいる。

(2020/02/21)

主催者がMWC2020開催を中止

(2020年2月11日 22:34)わずかな期間に主催者であるGSMAが、モバイル通信技術の展示会&セミナーであるMWC(Mobile World Congress)の開催中止を決定した。通信機器のEricssonが中止を早々と決めたのに続き、AmazonやNvidiaも中止を決めたことを2月11日に報じた。この記事掲載の後、Nokia、AT&T、Sprint、、BT(ブリティッシュテレコム)、ドイツテレコムなども中止を明らかにした。大手通信業者や通信機器メーカーなどが撤退を決めたことで主催者もMWCそのものを中止せざるを得なくなったのであろう。

以下は、参考のために2月11日に掲載した記事である。 (2020/02/13)

コロナウィルスで、モバイル展示会MWC出展取り消す企業が続出

スペインのバルセロナで毎年開催されていたモバイル通信技術の展示会&セミナーのMWC(Mobile World Congress)(図1)への出展取りやめが相次いでいる。今年は2月24日から27日に開催される予定だったが、2月4日に中国のZTEが出展取りやめを皮切りに、7日にはスウェーデンのEricssonが出展を中止すると発表した。

図1 MWCが開催されるスペイン・バルセロナの会場 筆者撮影

2月11日現在、出展・参加取りやめを表明したところは、米国のECサイトAmazonの他、AI向け半導体GPUを開発しているNvidia、韓国大手家電メーカーのLG、そして中国の大手家電メーカーTCL、さらに日本のソニーとNTTドコモなど。

MWCは、ソフトバンクやKDDIなどの通信オペレータや、CiscoやNokiaなどの通信機器メーカー、さらに通信機器に使う半導体メーカー、IPベンダー、通信機器に組み込むソフトウエアベンダー、OSやミドルウエアのソフトウエアベンダー、そして民生用のスマートフォンやタブレットなどのメーカー、クラウド上での通信サービスを展開するソフトウエアベンダーなどが参加するイベントだ。規模は東京ビッグサイトの2倍くらいはあろう。とにかくでかい。

特にEricssonの出展中止の影響は大きい。同社のブースはいつも巨大だ。Ericssonブース内はアポイントメントなしでは入れない。いつどこの誰が何人入場するのか、を事前に届けておく必要がある。まるで企業の受付のような構えであり、受付で承認をもらったモノだけが入ることを許される。Ericssonのブースというより建物の中に普通のブースが並んであり、参加者の興味によってモデルコースを用意している。通信オペレータ向けのコースや経営陣向けのコースなど、回り方や重点的に見るブースや、スキップするブースなど来場者の属性でコースが異なっている。

Ericssonの建物内のブースから離れた場所に休憩所もあり、そこで、ハムやチーズなどのつまみやサラダ、パン、ワイン、ジュースなどを楽しむことができる。もちろん、ブースの係員や案内人などから不明な点を教えてもらえる上に、そこに詳しく説明できる専門員がいなければ呼びよせてくれる。まさにEricssonのブースは小さな遊園地のような作りになっている。

海外の展示会は展示物を披露することが出展社の目的ではなく、顧客や潜在顧客と商談やディスカッションをすることである。4日間で20社の自分のクライアントに会って話ができる機会は簡単には作れない。技術営業の人間が5人いれば合計100社と面接(インタビュー)できるため、展示会ほど効率よく顧客を回れるシステムはない。だからこそ出展するのだ。Ericssonの建物には商談室が20室ほどあり、アポなしでは入れない。商談会であることが日本の展示会とは大きく違う。

今回は、MWCの会場内で開催されるセミナーGTIの開催も中止になった。GTIはインドのインドのBharti Airtelや中国のChina Mobile、米Sprint、ソフトバンク、そして英Vodafoneが中心メンバーとなって、双方向通信方式について話し合う会議であった。特に携帯電話のTDD(時分割二重)とFDD(周波数分割二重)方式について話し合っていた。周波数効率の良いTDDは特に中国が推進しており、今回のコロナウィルスのパンデミックのためにいち早く中止を表明していた。

MWCは通信業者の大きなイベントであるが、コロナウィルスのような蔓延しやすいパンデミックの原因がはっきりしている以上、リスク管理意識の高い企業はすぐに取りやめることを決意した。コロナウィルス発病者が中国に続き2番目に多い日本は、政府の遅い対応からわかるように、リスク管理の意識が極めて薄い国のようだ。

(2020/02/11)

オムロンが東京に開発工場を作った理由(わけ)

(2020年2月11日 14:37) 制御機器やセンサ、ヘルスケアなどの事業を手掛ける、京都のオムロンが、東京品川駅の近くに開発工場を設立した。東京に工場を作ったのは、東京が世界の玄関口だからだ。オムロンは世界36カ所にオートメーションセンター(ATC)を持っている。加えて、東京に本社を持つ企業は多い。この品川は世界で37番目の拠点となるという。

品川は、アジアと北米をつなぐ中間にある。ここにモノづくりのユーザー企業に来てもらい、「ユーザーの持つ課題を解決するためのソリューションを一緒に開発するためにこの工場を使ってもらう」ことを意図している。エンジニアだけではなく、ユーザー企業の経営陣もこのオートメーションセンターに来てもらいたい、とオムロン執行役員副社長兼インダストリアルオートメーションビジネスカンパニー社長の宮永裕氏(図1)は述べている。

図1 オムロン執行役員副社長兼インダストリアルオートメーションビジネスカンパニー社長の宮永裕氏 筆者撮影

オムロンは工場のオートメーションに強い。これを実現するための制御機器を20万点も持っている。これを生かし、さらに将来のモノづくりの革新を見据えて、制御機械の高速・高精度化を図るためにもっとintelligent(インテリジェント)に制御することで生産性向上につなげようとしている。制御機器にインストールしたソフトウエアも170種あり、工場の機械から発生するさまざまなデータを収集(integrated)・活用し学習させ、モノづくりの進化を狙う。さらに人と機械との新しい協調としてインタラクティブ(interactive)を掲げている。これらをまとめて、i-Automationと呼び、これが未来のオートメーションとしている。

ATC東京では、オムロンが誇る20万種以上の制御機器を高度にすり合わせた技術力とアプリケーションを組み合わせて、顧客の課題に合わせた解決策を実証することができる。加えて、これらの制御機器を導入するために必要な技術トレーニングも提供する。さらに協調ロボットや移動型ロボットなどを使った作業の検証もできる上、ユーザーの装置を持ち込み、ロボットを使った実験も行うことができるという。

最新の自動化するモノづくりを体感するだけではなく、実証、技術習得、開発まで、ワンストップでユーザーと一緒に開発することができる。モノづくりの現場は多品種少量生産が求められるようになっており、その割に熟練工の不足も同時に進行している。このため、これまでとは異なる革新的な自動化モノづくりを提供しようという訳だ。

東京は、日本経済の中心地であり、世界的な企業も集結しており、しかもアジアからと北米からのアクセスも良い。加えて、ビジネスの決定権のある経営陣も東京に常駐していることが多い。潜在顧客を取り込むには絶好の場所である。ここでビジネスを決めてもらうためにはモノづくりを基本とするオムロンにとって好都合である。

量産と違って、開発だけなら工場といえども広大な敷地は要らない。実証実験(PoC: Proof of Concept)するための設備を揃え、しかも工場の開発部門で使う最先端のオムロン製マシンを揃えておけば、マシンのショールームにもなる。もちろん今回の開発工場はショールームが目的ではない。実際に使ってみることができることが最大のウリだ。しかも最先端の高速・高機能なマシンが勢ぞろいしているため、これらのマシンを使ってPoCできると、実はIoTの利用促進といったデジタルトランスフォーメーションによる生産性向上の道のりが早くなる。

図2 オムロンのATCでは産業機械やロボットが生産ラインのPoCに使える 筆者撮影

オムロンが強い、PLC(Programmable Logic Controller)コントローラとサーボモータ制御、センサ、ロボット、安全性の5つの技術を持つ企業は他にはない、と宮永氏は言い切る。同社にはこれまでにも草津や刈谷にもATCを持つ。刈谷は言わずと知れたトヨタ自動車のティア1サプライヤーであるデンソーの本拠地だ。このATCにはトヨタの経営陣が来る。今後は次のクルマの工場についてコンセプトをディスカッションしたいという。

加えて、東京には半導体チップベンダーやディストリビュータ、OSベンダー、アプリケーションソフトウエアベンダーなどが集まっている。しかもIoTシステムを開発する場合のエコシステム、例えばIoTビジネス共創ラボなどの組織が揃っている。この環境を利用しない手はない。企業としていち早く生産性向上や働き方改革なども実現しやすい。開発工場が東京にあることの重要性をオムロンがいち早く見つけた、といえそうだ。

(2020/02/11)

国産ファブレス半導体スタートアップ、5nmのAIチップを開発

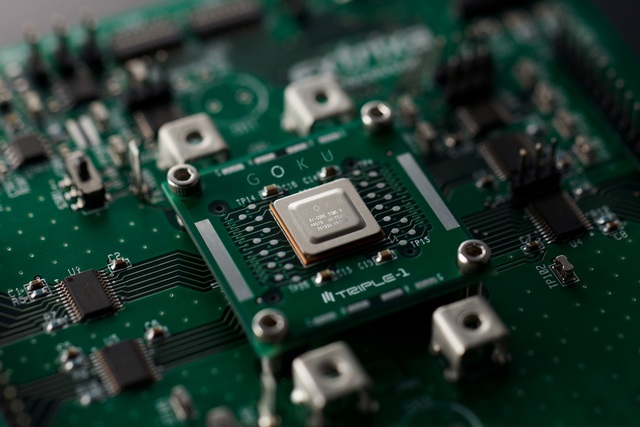

(2020年1月28日 23:22) 日本にもやっとファブレス半導体のベンチャーが登場した。半導体設計には時間もコストもかかる。それでも5nmという最先端の製造技術をTSMCに依頼して、AIコアを作り上げた。福岡市に本社を持つTRIPLE-1という名のスタートアップ企業だ。

図1 AIコアの試作チップ 出典:TRIPLE-1

TRIPLE-1は2016年11月に創業したスタートアップで、これまでも仮想通貨のマイニングするためのチップを開発しており、2018年には「KAMIKAZE」という名称のマイニングチップを開発していた。仮想通貨(英語では暗号通貨)では、毎日の取引結果を台帳に書き込むわけだが、先に書き込んだ人が仮想通貨をもらえる。仮想通貨の取引高は暗号化されているため、暗号を解くためには高速の計算機が必要になる。このため専用の半導体チップを使って高速の専用コンピュータを作るという訳だ。

「KAMIKAZE」はTSMCの7nmプロセスで製造した。暗号解読コンピュータは、演算器を超並列に多数並べることで解読するため、チップに集積するトランジスタ数はおのずから増加する。チップは大きくなればなるほど歩留まりが落ちるため、微細化することでできるだけ小さな面積で多数のトランジスタを集積する。このために当時最先端の7nmプロセスを使って集積回路ICを手に入れた。

昔は、半導体を手に入れるためには工場を建てることから始まった。しかし、ファブレスとファウンドリのビジネスモデルが確立した今、工場を持つ必要はなくなった。だからファブレスで顧客が欲しいと思える半導体製品のビジネスは十分に成り立つ。DRAMやNANDフラッシュのように大量生産型のコモディティ製品は、工場を持つ方がコスト的に有利だが、大量生産品を持たない場合はファブレスでなければコスト的に合わない。残念ながら、これまでの日本の半導体メーカーはシステムLSIという少量多品種製品の時代になっても工場を持つことに固執したため、コスト的に合わず(ラインが埋まらず)、割高の製品しか作れなくなっていた。だから国際競争で米国にも欧州にもアジアにも負けたのである。

TRIPLE-1はれっきとした国産のファブレス半導体メーカーだ。社員数はまだ30名ほどしかいないが、そのうちの7割が国内の大手にいた半導体設計エンジニアだ。大手の半導体メーカーはリストラを繰り返しているため、優秀なエンジニアを確保することはそれほど難しくはない。当然ながら技術のことは詳しい。会社設立3カ月後の2017年2月にはマイニングチップの設計仕様を検討し始め、わずかその1年後の2018年2月にはテープアウト(設計完了)した。そして2018年5月には初期量産ウェーハ投入にこぎつけ、暗号解読専用コンピュータまでも2018年12月に初期量産できるようになった。ものすごいスピードだ。

2019年9月には、AIコアの評価チップを開発、最近になってようやくその性能を評価できるようになったが、顧客のサンプル評価も同時に進めている。このAIコアもやはりTSMCに製造依頼したが、最先端の5nmで設計・製造した。AIチップは小さなMAC(積和演算)とメモリをセットにしたブロックを大量に超並列に配置している。このため、多数のトランジスタを小さく集積する必要があり、最先端の微細化技術でチップを小さくした。

今回開発したチップは、AIチップといえるほどまだMACの数は多くないが、このAIブロックコアの性能や消費電力を評価し成功の可能性が見えたら、今度はチップ製作へと移る。チップを依頼するのにはコストがかかるが、資金調達は社長の役割だ。社長の山口拓也氏は、資本金36億円を調達し、半導体チップビジネスの夢を描く。「どうせやるなら最先端技術を使いたい」と2番ではなく1番を目指す。微細化に向いたマイニングチップ、さらにAIチップと狙いは王道を行く。TRIPLE-1は、日本の半導体産業に久々に灯った明かりになる可能性を秘めている。

(2020/01/28)

早く買収されたい外資系の社員たち

(2020年1月28日 13:37) 1月中旬に東京ビッグサイトで開催された第12回オートモーティブワールドでは、これから買収されようとする企業の社員が早く買収されたいという声を聞き、彼らの気持ちの高まりを感じ取った。一方で、相乗効果のない事業部門でも買収提案されたら何が何でもそれを手放さない、という日本の企業経営者の姿勢との大きな差を見ることができた。

図 第12回オートモーティブワールドの一風景

ここで買収しようとしている企業がドイツのインフィニオンであり、買収されたいと社員が浮足立って期待が先走っている企業が米サイプレスだ。また、日本の企業経営者とは東芝のトップである。ガラスメーカーのHOYAが東芝の子会社で半導体製造装置を作っているニューフレアテクノロジーの買収を提案した時に示した東芝の経営者はまるで駄々っ子のようだった。

インフィニオンがサイプレスを買収するとクルマビジネスで極めて大きな効果がある。単に売上額の足し算によるものではない。互いに重なる製品はほとんどなく、しかも共にクルマ向け半導体事業に力を入れており、大きく伸びそうなことがはっきり見えるからだ。クルマメーカー(OEM)にはワンストップショッピングで製品ポートフォリオを示すことができ、それらを使ってシステムを提案できるのだ。これからの半導体ビジネスを先導するような仕掛けだといえる。

自動車産業は一番上にOEMがいて、その下にデンソーやボッシュ、コンチネンタルなどのティア1サプライヤ、その下に電子部品や半導体などのティア2サプライヤがいるという産業構造である。最近は半導体メーカーがOEMに直接、新しいシステムを提案するようになってきた。このため、開発するシステムを直接クルマメーカーに提案できることは極めて有利だ。OEMは提案内容のメリットを享受できるだけではなく、新しいハイテクをいち早く取り入れることができるからだ。かつてはBMWが、最近ではAudiが進取の気性ともいうべき新しもの好きなOEMである。

インフィニオンはパワー半導体だけではなく、レーダーやジャイロなどのセンサ半導体も持っており、ハイパワーのパワーマネジメントIC、さらにはセキュリティを担保するセキュリティマイコンにも強い。片やサイプレスはアナログ回路もプログラムできるマイコンのpSoCの評判が良くさまざまなセンサやインターフェイスIC、タッチセンサなどにも応用している。クルマでは、これからのコックピット向けにマイコンベースでグラフィックスを描画できるICや中小のパワーマネジメントICなどもある。クルマへの応用として両社の持つ全ての製品を使ったソリューション提案ができるのが最大の強みだ。このことは買収される側のサイプレスの社員が熟知しており、両社の相乗効果に大きな期待を寄せている。

ビッグサイトで開催されたこの展示会では、出展したサイプレスの社員が買収の決定をまだかまだかと待っている様子を感じ取れた。相乗効果で両社とも強くなれることをよくわかっているからだ。インフィニオンもこれでクルマ向け半導体のトップメーカーになれることで期待に胸を膨らましている。これほど相乗効果が期待できる買収も珍しい。

ところが、東芝の子会社であるニューフレアテクノロジーが買われることに東芝が断固として反対した姿勢は全く理解できない。東芝にとって相乗効果のない部門だからだ。先端半導体製造に必要な電子ビーム露光装置を設計・製造しているニューフレアは、自社内では使い道がない。他社に売るために電子ビーム露光装置を作っている。

ここにガラス製造のHOYAがニューフレアへの買収を提案した。ただ、いきなり買収提案したわけではない。HOYAは2017年からニューフレアテクノロジーとの提携話を東芝に持ち込んできていたが、肯定も否定もしない煮え切らない態度が続いていた。ところが2019年11月にいきなり東芝がニューフレアの株式をTOB(公開株式買付)で買うことを発表したため、その一月後にHOYAはニューフレアを買うためのTOBを仕掛けた。

HOYAは半導体製造に必要なガラスマスク(回路パターンを形成したガラス基板)とマスクブランクス(ガラス一面をメタルなどでマスクした基板)を製造しているが、マスクブランクスから電子ビーム露光装置で回路パターンを描く。HOYAは今、外部から電子ビーム露光装置を購入しているが、自社で装置を持っていれば、顧客からの要求で装置を改良したり発展させたりすることができる。半導体の微細化技術は最先端の7nmプロセスから、X線のように波長の短いEUVリソグラフィ技術を使うようになったが、そのマスクも電子ビーム露光装置が製造する。最先端の顧客にも対応でき、HOYAのビジネスは半導体関連分野で広がるはずだった。

東芝にとってはほとんど相乗効果がないのにもかかわらず、ニューフレアを大事に持つ意味はどこにあるだろうか。むしろHOYAは東芝が実施する株価よりも1000円も高く買うわけだから、今のうちに売却する方が良かったのではないか、と考えることはごく自然である。

これまで総合電機の経営者の姿を見てくると、自分で判断もその材料も持っていないのにもかかわらず、事業を手放さず持っていたいという気持ちが強いようだ。例えば、NECは半導体部門をNECエレクトロニクスとしてスピンオフさせたが、株式の8割以上を持っていた。親会社-子会社という関係を維持しているため、人事権も親会社が持つ。子会社が好きなように経営しても親会社が気に入らなければ子会社のトップはすぐに外へ飛ばされる。海外の優良企業の経営者ではこんな非合理なことはありえない。例えばフィリップスから独立したNXPセミコンダクターやリソグラフィのASMLなどは子会社ではなく、フィリップスの持つ株式は10%程度、現在はゼロになっている。スピンオフした以上、自分で稼ぐことが条件である。シーメンスから独立したインフィニオンも同様だ。経営者自身が理解できないビジネスは持たないことが原則だからだ。

日本ではひたすら様々な事業部を天下に収めることが経営者の仕事になっている。しかし、企業を成長させ、社員や株主がハッピーにさせることが経営者の使命ではないか。東芝はこれから10年間、どうやって成長させ社員や株主をハッピーにさせるのか、いつになったらその意志が発表されるのだろうか。

(2020/01/28)